Cloud native EDA tools & pre-optimized hardware platforms

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

-

Jan 31, 2018

Synopsys, Inc. (Nasdaq: SNPS), today announced availability of its Verification IP (VIP) and source code Test Suite for Arm® AMBA® ACE5 (AXI Coherency Extensions) and AXI5. Synopsys has...

-

Jan 30, 2018Latest release adds support for Scala and VB.NET, SEI CERT C Coding Standard, and enhanced Jenkins plugin

Synopsys, Inc. (Nasdaq: SNPS) today announced its Coverity® 2018.01 release, the newest version of its industry-leading static analysis tool, which analyzes source code to detect critical quality...

-

Jan 29, 2018Silicon-based Hardware Platform with Wide Range of I/O and Comprehensive Software Support Reduces Development Time for SoCs Targeting High-Performance Embedded Applications

Highlights: Quad-core ARC HS Development Kit operates at speeds up to 1GHz and offers a rich set of interfaces to enable early software development for ARC HS3x-based systems The Development Kit...

-

Jan 23, 2018Enables Mixed-Signal Products for Automotive to Test Themselves During Power-on

Highlights: Provides power-on self-test (POST) required for automotive applications Easy to deploy with few modifications to existing DFTMAX compression flows Checks for faults within specific...

-

Jan 17, 2018Two-year study explores the roles of information security leaders and how they are affected by organizational dynamics

Synopsys, Inc. (Nasdaq: SNPS) today published the inaugural CISO Report, the result of a two-year data-driven study exploring the roles of information security leaders and the organizational...

-

Jan 11, 2018Five-member board of experienced security executives to guide technical innovations of Synopsys security products and services

Synopsys, Inc. (Nasdaq: SNPS) today announced the formation of a Technical Advisory Board (TAB) to guide the technical direction of the Synopsys Software Integrity Group's security products and...

-

Jan 10, 2018Acquisition Enables Synopsys to Provide a Broad Non-Volatile Memory IP Offering Optimized to Meet Performance, Power, and Area Targets for a Wide Range of Applications

Highlights Kilopass Technology's one-time programmable (OTP) non-volatile memory (NVM) IP has been integrated by more than 170 customers into more than 400 SoC designs, and shipped in more than 10...

-

Jan 10, 2018

Synopsys, Inc. (Nasdaq: SNPS) today announced that Aart de Geus, Chairman and Co-CEO, will speak at the 20th Annual Needham Growth Conference, in New York, on Jan. 17, 2018. This event will be...

-

Dec 14, 2017Helic Tools Integrated into Synopsys Custom Design Platform to Accelerate Robust Design

Highlights: Synopsys' Custom Compiler has been integrated with Helic's RF device synthesis, EM parasitic extraction, and modeling software Integrated solution blends parasitics from Synopsys'...

-

Dec 13, 2017IC Validator Physical Signoff and StarRC Extraction Signoff Displace Incumbent Tools

Highlights: IC Validator delivers superior productivity for DRC and LVS signoff of mixed signal designs StarRC's ultra-scalable extraction solution provides 10X runtime advantage with superior...

-

Dec 12, 2017The Synopsys Static Analysis (Coverity) Solution Ranks Highest in Current Offering and Strategy Categories

Synopsys, Inc. (Nasdaq: SNPS) today announced it has been positioned as a leader in The Forrester Wave™: Static Application Security Testing, Q4 2017. The report provides an in-depth analysis...

-

Dec 12, 2017With Version 2017.12, Designers Can Simulate Pixel Light Technology to Improve Headlamp Safety and Efficiency

Synopsys, Inc. (Nasdaq: SNPS) today announced the latest release of its LucidDrive® software product, which allows designers to simulate the performance of automotive headlamps when driving at...

-

Dec 11, 2017

Synopsys, Inc. (Nasdaq: SNPS) has completed its acquisition of Black Duck Software, Inc., a privately held leader in automated solutions for securing and managing open source software. Software...

-

Dec 7, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that it has entered into accelerated share repurchase agreements (ASRs) with JPMorgan Chase Bank, National Association and MUFG Securities EMEA plc....

-

Dec 3, 2017In addition, 48 Percent for Survey Respondents Believe Lack of Skilled Security Personnel or Training Is Key Secondary Challenge

Synopsys, Inc. (Nasdaq: SNPS) today announced the results of a survey of 244 IT professionals that revealed customer-facing web and mobile applications present the highest security risk to...

-

Nov 30, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that Trac Pham, chief financial officer, will speak at the Nasdaq 37th Investor Program, in London, on December 5, 2017. This event will be broadcast...

-

Nov 30, 2017DesignWare IP Provides Secure, High-Quality Digital Video and Audio Link for 8K Resolution

Highlights: Complete HDMI 2.1 IP solution with HDCP 2.2 content protection includes controllers, silicon-proven PHYs, verification IP, IP Prototyping Kit, and IP subsystem for fast integration...

-

Nov 29, 2017

Q4 2017 Financial Highlights Revenue: $696.6 million GAAP loss per share: $0.80 Non-GAAP earnings per share: $0.69 FY 2017 Financial Highlights Revenue: $2.725 billion GAAP earnings per share:...

-

Nov 20, 2017Version 2017.09 Shortens the Design-Analysis Cycle and Allows More Time to Explore Automotive Lighting Design Solutions in the CATIA V5 Environment

Highlights: Support for configuring and running multiple optical simulations improves the efficiency of analyses for a range of automotive lighting functions, from high and low beams to signal...

-

Nov 15, 2017DesignWare EV6x Processor's Tightly Integrated Vector DSP and CNN Engines Power Inuitive's NU4000 3D Imaging and Vision Processing SoC

Highlights: Inuitive selected the DesignWare EV6x Embedded Vision Processor for its high vector DSP and neural network performance in a minimal silicon footprint Combination of dual vector DSPs...

-

Nov 13, 2017Partnership Enables Advancement of ZeBu Server as the Leading SoC Emulation Tool for the Automotive Industry

Synopsys, Inc. (Nasdaq: SNPS) and the French Alternative Energies and Atomic Energy Commission (CEA), a key player in technology research, today announced their new partnership based on Synopsys...

-

Nov 8, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced it will report results for the fourth quarter and fiscal year 2017 on Wednesday, Nov. 29, 2017, after the market close. A conference call to review...

-

Nov 2, 2017

Synopsys, Inc. (Nasdaq: SNPS) and Black Duck Software, Inc. have signed a definitive agreement for Synopsys to acquire privately held Black Duck, a leader in automated solutions for securing and...

-

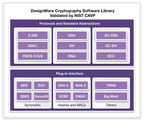

Nov 1, 2017Successful Testing of DesignWare Cryptography Software Library Enables Development of Highly Secure IoT Systems

Highlights: DesignWare Cryptography Software Library includes a suite of widely used encryption and certificate processing functions required for embedded applications Secure functions that passed...

-

Oct 31, 2017Enhanced BIST and Repair Algorithms for 7-nm FinFET Processes Increase Memory IP Test Coverage and Accelerate Power-On Initialization

MOUNTAIN VIEW, Calif., Oct. 31, 2017 Highlights Index-based repair capabilities in STAR Memory System cut memory repair cycles from more than 1000 to fewer than 100 cycles by testing only faulty...

-

Oct 31, 2017Company Standardizes on TetraMAX II Solution to Create Manufacturing Tests for All Designs

Highlights: TetraMAX II ATPG reduced test generation runtime by an order of magnitude, from an overnight run to less than one hour, while producing 50 percent fewer patterns DecaWave met their...

-

Oct 31, 2017Report highlights progress over past decade, identifying key indicators of project maturity and underscoring the importance of measuring risk

Synopsys, Inc. (Nasdaq: SNPS) today released the 2017 Coverity® Scan Report, which examines Open Source Software (OSS) quality and security data collected over the past decade through Coverity...

-

Oct 30, 2017ASIL D Ready Certified DesignWare Embedded Test and Repair IP Speeds Functional Safety Qualification for Automotive ADAS Applications

Highlights Validated solution, including DesignWare STAR Memory System, DesignWare STAR Hierarchical System, DFTMAX LogicBIST software qualification kit, and ARC HS processor, ensures high test...

-

Oct 30, 2017Provides Highest Degree of Safety Related Confidence and Accelerates Functional Safety Qualification

Highlights: All Synopsys test platform products can be confidently used for functionally safe automotive systems Test platform tools, tool qualification report and IP certification accelerate ISO...

-

Oct 26, 2017Recognition for Leadership in the Optics Industry and The Optical Society

Synopsys, Inc. (Nasdaq: SNPS) today announced that George Bayz, vice president of Synopsys' Optical Solutions Group, has been elected as a Fellow Member of The Optical Society (OSA). The OSA...

-

Oct 25, 2017Program's Goal is to Advance Superconductor Design and Propel Electronics Beyond CMOS

Highlights: Synopsys will enhance its state-of-the-art EDA tool flow to support ultra-low temperature superconducting technology Increasing the scale, efficiency, and quality of Superconducting...

-

Oct 23, 2017Comprehensive Synopsys Platform Enables Accelerated Verification of High-Performance, Low-Power RISC-V Processors and SoCs

Synopsys, Inc. (NASDAQ: SNPS) today announced that SiFive, the first fabless provider of customized, open-source-enabled semiconductors, has selected the Synopsys Verification Continuum™...

-

Oct 18, 2017New Virtualizer Design Kits Enable Automotive Tier 1 and OEM Companies to Start Software Development, Integration and Test Before Silicon

Synopsys, Inc. (Nasdaq: SNPS), today announced the extension of its multiyear Center of Excellence (CoE) program with NXP and availability of Virtualizer™ Development Kits (VDKs) for NXP S32...

-

Oct 17, 2017Acquisition Adds One-Time Programmable Non-Volatile Memory IP to DesignWare NVM IP Offering

Highlights Sidense's one-time programmable (OTP) non-volatile memory (NVM) IP offers a robust standard CMOS implementation, small footprint, low power, and broad foundry support Sidense's OTP NVM...

-

Oct 9, 2017Release 2017.09 of the RSoft Product Family Now Available

Highlights: S-Matrix/PDK Generation Utility for efficient, multi-level photonic integrated circuit design and analysis Increased simulation speeds of silicon photonics components by 100x or more...

-

Oct 9, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced it will host the annual BSIMM Community Conference in Scottsdale, Arizona on October 9-11. The event will gather more than 200 representatives from...

-

Oct 5, 2017Native SystemVerilog USB VIP Features Built-in Coverage, Verification Plan, Protocol-Aware Debug and Source Code Test Suites

Synopsys, Inc. (NASDAQ: SNPS) today announced the availability of the industry's first verification IP (VIP) and UVM source code test suite to support the latest USB 3.2 specification. USB 3.2...

-

Oct 5, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced it will present a workshop with customer Schneider Electric focusing on "Building Security In" at the Les Assises conference in Monaco on October 12....

-

Sep 24, 2017Reference Flow for Silicon-Proven Design Platform Accelerates Path to Lower Power and Design Cost

Highlights: Samsung Foundry's 28FDS process is ideal for IoT, mobile and automotive applications Comprehensive certification includes digital, custom and SPICE tools of the Synopsys Design...

-

Sep 20, 2017DesignWare Interface and Analog IP Enables Faster Time-to-Volume for Energy-Efficient IoT and Mobile SoCs

Highlights: DesignWare Interface IP portfolio for GLOBALFOUNDRIES' 22FDX® process includes USB 3.1/3.0/2.0, USB-C 3.1/DisplayPort, PCI Express® 3.1/2.0 and HDMI 2.0 TX PHYs DesignWare Data...

-

Sep 20, 2017Certification Enables Optimized Implementation and Predictable Signoff

Highlights: Certified IC Compiler II, IC Validator, PrimeTime, and StarRC tools for implementation and signoff of 22FDX designs Based on silicon-proven RTL-to-GDS 22FDX Foundry Reference Flow,...

-

Sep 20, 2017Latest Iteration of the Building Security in Maturity Model Shows More Organizations Jumpstarting their Software Security Initiatives with Assessments and Improving Over Time

Synopsys, Inc. (Nasdaq: SNPS) today released BSIMM8, the latest version of a leading software security maturity model, which is based on real-world data and helps organizations plan, execute, and...

-

Sep 19, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that John Steven, senior director at the Synopsys Software Integrity Group, will deliver a keynote at AppSec USA 2017 in Orlando, Florida on September 21.

-

Sep 19, 2017DesignWare ARC Secure IP Subsystem Provides Programmable Hardware Root of Trust to Protect Against Malware, Tampering and Exploitation of Communication Protocols in SoCs

Highlights: Pre-verified DesignWare ARC Secure IP Subsystem provides a trusted hardware and software SoC environment that protects against malicious attacks targeting mobile, IoT and automotive...

-

Sep 19, 2017Comprehensive Foundry Reference Flow Leverages Industry-leading IC Compiler II

Highlights: Designers can confidently implement their 22FFL-based ICs with the Intel® Custom Foundry certified digital and custom tools from the Synopsys Design Platform The comprehensive digital...

-

Sep 18, 2017Materials Modeling Enables Semiconductor Manufacturers to Save Time and Cost for Advanced Process Node Development

Highlights: QuantumWise solution reduces time and cost by enabling earlier co-optimization of materials, processes, devices, and circuits for 5nm and beyond Rigorous modeling of materials provides...

-

Sep 18, 2017Platform Consisting of ARC Data Fusion IP Subsystem, Peripherals, Operating System and Software Development Tools Enables Immediate Productivity

Highlights: DesignWare ARC IoT Development Kit includes the necessary hardware and software to speed software development and debugging of ARC EM processor-based designs Silicon-proven hardware...

-

Sep 18, 2017IoT Platform Accelerates Designs for IoT Edge Devices with Synopsys Silicon-Proven ARC Data Fusion IP Subsystem, Brite ASIC Design Services and SMIC 55-nm Ultra-Low Power Process

Highlights: The IoT platform based on Synopsys' ARC Data Fusion IP Subsystem and interface IP, implemented by Brite's expert design services for SMIC's 55-nm ultra-low power process accelerates...

-

Sep 18, 2017TSMC Awards recognize Synopsys' Collaboration on Interface IP, Joint Development of 7nm FinFET Plus and 12FFC Design Infrastructures and Joint Delivery of an Automotive Design Enablement Platform

Highlights: TSMC selects Synopsys as its "Partner of the Year" for interface IP and tool enablement for the 7th consecutive year TSMC has certified Synopsys' digital and custom implementation...

-

Sep 14, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that it has entered into an accelerated share repurchase agreement (ASR) with HSBC, to repurchase an aggregate of $100 million of Synopsys stock. The...

-

Sep 13, 2017Combination of Alango's Far-Field Voice Enhancement Software Technologies and Synopsys' ARC IP Subsystem Provides Ideal Low-Power Solution for Voice-Controlled Devices

Highlights: Alango's Voice Enhancement Package (VEP) offers multi-microphone beamforming array and echo cancellation technologies to enhance speech recognition performance in voice-controlled...

-

Sep 12, 2017Logic Libraries and Embedded Memories for TSMC 40LP and 40ULP eFlash Processes Improve Energy Efficiency for IoT Devices

Highlights: DesignWare Logic Libraries offer power optimization kits, multi-bit flip-flops and ultra-low leakage standard cells to achieve lowest power with near threshold operation High-density...

-

Sep 11, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced it will showcase its Software Integrity Platform at GovernmentWare 2017 (GovWare) in Singapore from September 19 to 21, 2017. GovWare is one of the...

-

Sep 11, 2017DesignWare Foundation and Interface IP on TSMC 7-nm Process Technology Enables Faster Time-to-Market for Mobile, Automotive and High-Performance Computing SoCs

Highlights: Synopsys' successful tape-outs of DesignWare Interface PHY IP for TSMC's 7-nm process include USB 3.1/2.0, DisplayPort 1.4, PCI Express 4.0/3.1, DDR4, MIPI D-PHY, Ethernet and SATA 6G,...

-

Sep 11, 2017Platform-Wide Certification for TSMC's Latest Advanced-Process Technology

Highlights: Design Compiler Graphical and IC Compiler II place-and-route validated on multiple 7-nm FinFET Plus high-performance production designs PrimeTime and StarRC advanced variation modeling...

-

Sep 11, 2017Platform-Wide Enhancements Across Digital and Custom Design Tools Deliver a Production-Ready Flow

Highlights: Synopsys Design Platform is certified for TSMC's innovative 12-nm process technology with customer validation on multiple production tape-outs PDK availability for the Custom Compiler...

-

Sep 8, 2017Updating GAAP targets; No Change to Non-GAAP targets

Synopsys, Inc. (Nasdaq: SNPS) today announced that its board of directors has approved a plan to repatriate approximately $775 to $850 million of cash currently held offshore during the fourth...

-

Sep 6, 2017ARC Processor Summit Attendees Will Learn about Solutions to Address Design Challenges in IoT Security, Automotive Safety and Embedded Vision Applications

WHEN: Tuesday, September 26 from 8:30 a.m. to 7:00 p.m. WHERE: Santa Clara Marriott, 2700 Mission College Boulevard, Santa Clara, CA REGISTER: www.synopsys.com/ARCsummit Synopsys, Inc. (Nasdaq:...

-

Sep 5, 2017Latest Release Offers Enhanced MTF Optimization and Visualization of Compact Optical Devices

Synopsys, Inc. (Nasdaq: SNPS) today announced version 11.1 of its CODE V® optical design software, which includes enhancements to the software's industry-leading capabilities for the design,...

-

Sep 5, 2017Samsung SARC Selects Synopsys as Primary Verification Solution for Advanced Mobile Processor DesignsComprehensive Synopsys Platform Enables Accelerated Verification of High-Performance, Low-Power CPU, GPU and System IP for Mobile SoCs

Synopsys, Inc. (NASDAQ: SNPS) today announced that Samsung SARC has selected the Synopsys Verification Continuum™ platform as its primary verification solution for their high-performance,...

-

Aug 30, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that Dave DeMaria, vice president of Corporate Marketing, will speak at the 2017 Citi Global Technology Conference in New York, on September 7, 2017,...

-

Aug 29, 2017New Bluetooth Low Energy PHY Delivers Up to 60 percent Smaller Area for Low-Power IoT Designs

Highlights: Synopsys' silicon-proven DesignWare Bluetooth Low Energy Link Layer and PHY IP solution is Bluetooth 5 qualified to ensure compliance and interoperability PHY IP in 40-nm process...

-

Aug 24, 2017In addition, 41 Percent Believe Lack of Skilled Security Personnel or Training is Key Secondary Challenge

Synopsys, Inc. (Nasdaq: SNPS) today announced the results of a survey of 270 IT security professionals, which found that almost half (48 percent) viewed customer-facing web applications as the...

-

Aug 16, 2017Q3 2017 Financial Highlights

Synopsys, Inc. (Nasdaq: SNPS) today reported results for its third quarter of fiscal year 2017. Synopsys reported revenue of $695.4 million, compared to $615.2 million for the third quarter of...

-

Aug 9, 2017Analysis of 4.8 Billion Fuzz Tests Identified 6.6 Seconds as the Average Time to First Failure for the Least Mature Protocol

Synopsys, Inc. (Nasdaq: SNPS), today released its fuzzing report, which provides deep analysis on potential zero-day exploits in the open source protocols and common file formats used across six...

-

Aug 8, 2017CNN-based Image Classification Software with DesignWare EV6x Vision Processor IP Delivers High Recognition Rate with Small Memory Footprint for Power-Constrained Devices

Highlights: Combination of DesignWare EV6x Vision Processors with Morpho Scene Classifier software delivers real-time image analysis and classification for power-sensitive applications such as...

-

Aug 8, 201718th Annual Competition Recognizes Student Achievements in Optical Design

Synopsys, Inc. (Nasdaq: SNPS) today announced that students from the University of Arizona and University of Rochester received awards for their entries in the 2017 Robert S. Hilbert Memorial...

-

Aug 2, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced it will report results for the third quarter fiscal year 2017 on Wednesday, Aug. 16, 2017, after the market close. A conference call to review the...

-

Aug 1, 2017DesignWare PHY IP for LPDDR4, MIPI, PCI Express and Ethernet Delivers High Reliability for ADAS and Autonomous Vehicle SoCs

Highlights: AEC-Q100 designed and tested DesignWare IP includes LPDDR4, MIPI D-PHY, PCI Express 3.1 and Ethernet on 16-nm FinFET process technologies IP with available test reports meets Grade 1...

-

Jul 26, 2017HAPS-80 Delivers 2X Performance and 2X Capacity Compared to Prior Generation

Synopsys, Inc. (Nasdaq: SNPS) today announced that MediaTek, a leading fabless semiconductor company, has adopted Synopsys' HAPS®-80 prototyping system, part of the Verification Continuum™...

-

Jul 25, 2017New DesignWare HBM2 Controller, PHY and Verification IP Enables High-Bandwidth, Power-Efficient Systems

Highlights: Complete HBM2 IP solution, including PHY, controller and verification IP, reduces integration risk while minimizing time-to-market DesignWare IP implementation supports data rates up...

-

Jul 13, 2017Latest Product Updates Expand Coverage for New Programming Languages and MISRA Compliance, Improve Integration Capabilities and Increase Flexibility

Synopsys, Inc. (Nasdaq: SNPS) today announced key updates to its Software Integrity Platform that are designed to help companies build security and quality into their software while reducing...

-

Jun 29, 2017Industry Experts Explore DevOps Security, IoT Security across Verticals and How to Build Security into the Software Development Lifecycle

Synopsys, Inc. (Nasdaq: SNPS) today announced it will host codenomi-con USA 2017, an exclusive event that gathers an elite group of cybersecurity experts, on Tuesday, July 25, during Black Hat USA...

-

Jun 28, 2017VC Formal Delivers Faster Convergence for Complex Multi-Functional Product Designs

Synopsys, Inc. (Nasdaq: SNPS) today announced that Kyocera, a leading supplier of telecommunications equipment, information equipment, semiconductor packages and electronic components, has...

-

Jun 26, 2017Enhanced DesignWare EV6x Family Delivers Up to 4.5 TeraMACs/sec for Real-Time Vision Processing

Highlights: DesignWare EV6x Vision Processors integrate up to four 512-bit vector DSPs and a CNN engine, providing scalable performance for a wide range of current and emerging embedded vision...

-

Jun 20, 2017Enablement Includes Industry-Leading IC Compiler II P&R Solution and DesignWare Embedded Memory IP

Highlights: Synopsys Design Platform supports advances in GLOBALFOUNDRIES' 7-nm low-power technology and Self-Aligned Double Patterning (SADP) IC Compiler II enhancements include router...

-

Jun 19, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced the availability of its Verification IP (VIP) and source code test suite for ARM® AMBA® 5 Coherent Hub Interface (CHI) Issue B. Synopsys VC VIP for...

-

Jun 19, 2017Exclusive Product Integration To Combine Power And Reliability Signoff Solution With Physical Implementation Solution For In-Design Analysis To Spur Future Smart Product Development

ANSYS (NASDAQ: ANSS) and Synopsys (NASDAQ: SNPS) will enable customers to accelerate the next generation of high-performance computing, mobile and automotive products thanks to a new partnership...

-

Jun 16, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that its Board of Directors has replenished its existing stock repurchase authorization back to $500 million. "Synopsys is committed to driving...

-

Jun 15, 2017Next-generation Formal Verification Technology Uniquely Positioned for Performance and Capacity Required for Complex SoCs

Synopsys, Inc. (Nasdaq: SNPS) today announced that Toshiba has deployed Synopsys' VC Formal™ solution as their SystemVerilog Assertion (SVA) based formal verification solution. VC Formal...

-

Jun 14, 2017World's Leading Solution Provider of Video Surveillance[1] Deploys Synopsys Solutions to Build Security and Quality into Its Software Development Lifecycle and Supply Chain

Synopsys, Inc. (Nasdaq: SNPS) today announced it was selected by Dahua Technology, a leading solution provider in the global video surveillance industry, to enhance the security of its Internet of...

-

Jun 8, 2017Online Access to Comprehensive Suite of Free and Open Source Software and Tools Provides One-Stop Shop for Software Developers Programming ARC Processor-based Devices

Highlights: Comprehensive suite of free and open source software and tools for ARC processors cataloged and accessible from embARC.org provides developers with access to drivers, middleware and...

-

Jun 7, 2017

Synopsys, Inc. (Nasdaq:SNPS), today announced that STMicroelectronics selected and standardized on Synopsys VC Formal, as their formal verification solution for advanced microcontroller designs....

-

Jun 7, 2017

Synopsys, Inc. (Nasdaq: SNPS), will showcase its Silicon to Software™ solutions at the Design Automation Conference (DAC) in Austin, Texas, June 19 – 21, 2017. Synopsys' program includes...

-

Jun 6, 2017New DesignWare CCIX Controller, PHY and Verification IP Supports Speeds Up to 25Gbps and Enables Faster Data Access

Highlights: Complete CCIX IP solution supports cache coherency, allowing faster and more efficient sharing of memory between processors and accelerators Reliability, availability and...

-

Jun 6, 2017Analysis of More Than 120,000 Applications Found that Half of Third-Party Software Components in Use Are Outdated

Synopsys, Inc. (Nasdaq: SNPS) today released its report, "The State of Software Composition 2017," which analyzed real-world data to investigate the security of the software supply chain one of...

-

Jun 5, 2017Solution enables secure, remote lifecycle management for automotive, IoT and mobile applications

SUNNYVALE, Calif. – June 5, 2017 – Rambus Inc. (NASDAQ: RMBS) and Synopsys, Inc. (NASDAQ: SNPS) today announced a new collaboration to accelerate the adoption of advanced security platforms...

-

Jun 5, 2017Demonstration Proves Successful System Bring-Up and 16 GT/s Data Transfer of the DesignWare IP for PCI Express 4.0 Specification Targeting High-Performance Cloud Computing Designs

Highlights: The host, including the DesignWare Root Complex IP for PCI Express 4.0 specification, executes full initialization across the PCI Express link at 16 GT/s with the Mellanox ConnectX-5...

-

May 31, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that Ralf Huuck, director and senior architect for the Synopsys Software Integrity Group, will speak at Infosecurity Europe in London, 6-8 June 2017....

-

May 31, 2017

Synopsys, Inc. (Nasdaq:SNPS) today announced that Trac Pham, CFO, will speak at the Baird Global Consumer, Technology and Services Conference in New York, on June 8, 2017, at the InterContinental...

-

May 31, 2017Complete Compliant MIPI Display Solution Reduces Data Transmission Bandwidth for Mobile, Virtual Reality and Automotive SoCs

Highlights: Complete DesignWare MIPI DSI Host Controller with VESA DSC encoder and MIPI D-PHY easily integrates into application processors with less risk Integrated MIPI display IP reduces memory...

-

May 30, 2017ZeBu Server Enables Hardware and Software Teams to Work in Parallel, Saving Months on Schedules

Synopsys, Inc. (Nasdaq: SNPS) today announced that its ZeBu® Server emulation system has been selected and deployed by Konica Minolta as their standard hardware platform for verification and...

-

May 28, 2017New Optimized QuickStart Implementation Kits To Help Designers Quickly Achieve Target QoR Using Synopsys Design Platform

Highlights: Early adopters of ARM's latest IP – ARM Cortex-A75 and Cortex-A55 CPUs and Mali-G72 GPU – successfully tape-out using Synopsys' Design Platform, including Design Compiler...

-

May 26, 2017

Synopsys, Inc. (Nasdaq: SNPS) today announced that it has entered into an accelerated share repurchase agreement (ASR) with JPMorgan Chase Bank, National Association, to repurchase an aggregate of...

-

May 25, 2017Survey of Medical Device Manufacturers and Healthcare Delivery Organizations Reveals Industry's Lack of Confidence and Alignment in Securing Medical Devices

Synopsys, Inc. (Nasdaq: SNPS) today released the results of the study "Medical Device Security: An Industry Under Attack and Unprepared to Defend," which found that 67 percent of medical device...

-

May 24, 2017Synopsys Design Platform is Ready for Early Engagement with Mutual Customers

Highlights: 8LPP and 7LPP implementation flows fully enabled in IC Compiler II place and route, Design Compiler Graphical synthesis, IC Validator physical signoff and StarRC extraction tools 8LPP...

-

May 24, 2017Silicon-Proven IP Portfolio Provides Low-Risk Path to Silicon Success for SoC Designs on Samsung's Advanced Process Technologies

Highlights: DesignWare Interface IP portfolio for Samsung 14LPP and 10LPP processes includes USB 3.1/3.0/2.0, PCI Express 4.0, HDMI 2.1/2.0, LPDDR4 and DDR4 IP development builds on long history...

-

May 24, 2017IC Validator delivers physical signoff in hours with massively parallel architecture

Highlights: Certified 10LPP physical signoff runsets are available for DRC, LVS and metal fill Faster design closure achieved with timing-aware In-Design physical signoff within Synopsys' IC...

-

May 24, 2017Synopsys Custom Design Platform Certified for IoT, Mobile Computing and Automotive Applications

Highlights: Samsung's certification of Synopsys Custom Platform for 28FDS includes HSPICE circuit simulation, Custom Compiler layout implementation, StarRC parasitic extraction and IC Validator...

-

May 23, 2017DesignWare ARC HS4x Family Delivers Twice the Signal Processing Performance of Previous ARC HS Cores with Integrated DSP Capability

Highlights: New ARC HS4x and HS4xD processors with dual-issue architecture increase RISC performance by 25 percent compared to the popular ARC HS3x family while adding 2x higher DSP performance...