MOUNTAIN VIEW, Calif., Oct. 30, 2017 /PRNewswire/ --

Highlights

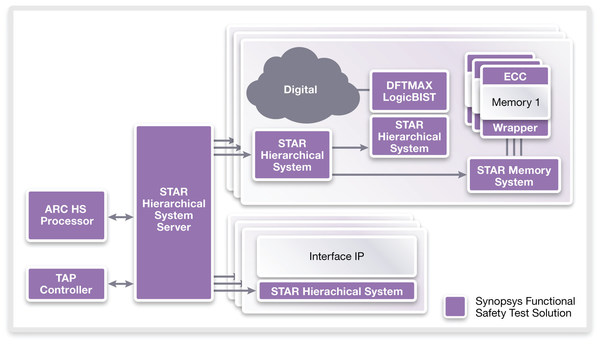

- Validated solution, including DesignWare STAR Memory System, DesignWare STAR Hierarchical System, DFTMAX LogicBIST software qualification kit, and ARC HS processor, ensures high test coverage for automotive systems

- DesignWare ARC HS processor functions as an on-chip safety manager for intelligent periodic and mission mode testing

- Test capabilities for embedded memories, logic blocks, and analog and mixed-signal IP provide high defect coverage for safety critical applications

- Solution enables full lifecycle testing of automotive SoCs from design, early silicon bring-up and production test to field deployment, which is essential for every automotive IC design

Synopsys, Inc. (Nasdaq:SNPS) today introduced a validated built-in-self-test (BIST) and repair IP solution to enable designers to achieve the most stringent levels of functional safety for automotive system-on-chips (SoCs). The complete solution includes the ASIL D Ready Certified DesignWare® STAR Memory System®, STAR Hierarchical System, and DFTMAX™ LogicBIST software qualification kit, as well as ARC® HS processors, providing test and repair of memory and logic blocks with automatic test integration and validation of analog/mixed-signal IP. By providing a pre-verified functional safety test solution, Synopsys is helping designers ensure high test coverage, achieve low defective parts per million (DPPM), and reach the required automotive safety integrity levels (ASILs) of their automotive designs.

"Safety critical automotive SoCs need to control run time scheduling, manage switching activity, and monitor the status of the logic and memory BIST," said Christophe Eychenne, DFT architect at Bosch. "Synopsys' ASIL D Ready Certified functional safety test solutions can fully support our requirements for high detection of logic and memory faults, self-test power up, and mission mode testing of our ADAS SoCs."

Synopsys' functional safety test solution leverages an industry-standard IEEE1500/1687-based infrastructure to reduce integration risk and offers multiple configurations to balance SoC test time, floor planning challenges, and system constraints. The solution includes complete test and repair capabilities for on-chip and CPU/GPU memories, logic blocks, and analog/mixed signal IP:

- DesignWare STAR Memory System offers memory BIST and repair capabilities with support for early silicon debug and in-field diagnostics using algorithms optimized for FinFET-specific transistor defects. Advanced STAR error correction code (ECC) circuitry detects and corrects single-bit and multi-bit upsets to improve reliability during in-system operation.

- DFTMAX LogicBIST software qualification kit provides a synthesis-based solution for rapid in-system self-test of digital circuits, enabling design teams to converge quickly on quality, cost goals, and functional safety requirements.

- DesignWare STAR Hierarchical System ensures high coverage using hierarchical test for IP block integration and enables re-use of IP patterns. Automatic test integration and validation with dynamic test scheduling optimize test time and power consumption, even post silicon. The STAR Hierarchical System detects process variation and device aging (soft monitoring) with its on-chip Measurement Unit feature.

- DesignWare ARC HS processor selects and activates tests by functioning as an on-chip safety manager. The interface between the ARC HS processor and other solution components has been optimized and validated to enable initiation and scheduling of the BIST activities and can be fully controlled by system software.

"As connected vehicles take on more autonomous tasks, test solutions must also advance to ensure the safety, longevity, and reliability of the entire system," said John Koeter, vice president of marketing for IP at Synopsys. "Synopsys' comprehensive functional safety test solution gives designers a fast, efficient method of integrating high-coverage test capabilities, enabling designers to meet the most stringent ISO 26262 requirements and accelerate development of their automotive SoCs."

Availability & Resources

The STAR Memory System, STAR Hierarchical System, DFTMAX LogicBIST and ARC HS processor family are available now.

- View the webinar: Addressing Functional Safety in SoCs with Test Solutions

- Learn more about STAR Memory System, STAR Hierarchical System, DFTMAX LogicBIST software qualification kit, and ARC HS processor family

About DesignWare IP

Synopsys is a leading provider of high-quality, silicon-proven IP solutions for SoC designs. The broad DesignWare IP portfolio includes logic libraries, embedded memories, embedded test, analog IP, wired and wireless interface IP, security IP, embedded processors, and subsystems. To accelerate prototyping, software development and integration of IP into SoCs, Synopsys' IP Accelerated initiative offers IP prototyping kits, IP software development kits, and IP subsystems. Synopsys' extensive investment in IP quality, comprehensive technical support and robust IP development methodology enable designers to reduce integration risk and accelerate time-to-market. For more information on DesignWare IP, visit www.synopsys.com/designware.

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day. As the world's 15th largest software company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and is also growing its leadership in software security and quality solutions. Whether you're a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing applications that require the highest security and quality, Synopsys has the solutions needed to deliver innovative, high-quality, secure products. Learn more at www.synopsys.com.

Editorial Contact:

Monica Marmie

Synopsys, Inc.

650-584-2890

monical@synopsys.com

SOURCE Synopsys, Inc.