Cloud native EDA tools & pre-optimized hardware platforms

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

| Su | Mo | Tu | We | Th | Fr | Sa |

|---|---|---|---|---|---|---|

-

Jul 13, 2016DesignWare IP Reduces USB Silicon Area by Up to 50 Percent with Near 0 W Standby Power Consumption for Longer Battery Life

Highlights: DesignWare USB 2.0 Type-C solution, including controllers and PHYs, reduces USB silicon area by up to 50 percent on ultra-low power 40-nm and 55-nm processes Extends battery life with...

-

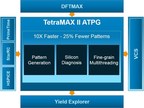

Jul 12, 2016New ATPG Engines Reduce Test Cost, Pattern Count by 25 Percent with Order of Magnitude Faster Runtime

Highlights: Order of magnitude faster ATPG ensures on-time availability of patterns for testing first silicon samples Significant pattern reduction enables designers to reduce test cost or...

-

Jul 12, 2016Independent Functional Safety Evaluation Provides Highest Level of Safety-Related Tool Confidence

Highlights: Tool certification accelerates ISO 26262 functional safety qualification for automotive ICs up to the most stringent safety requirements for ASIL D Enables automotive IC design teams...

-

Jul 12, 2016New ATPG Engines Substantially Reduce Test Pattern Count for Lower Test Cost

Highlights: Evaluation of TetraMAX II demonstrated an order of magnitude speedup in runtime Achieves significant test-pattern-count reduction without impacting test coverage Synopsys, Inc....

-

Jul 12, 2016New ATPG Solution Reduces Pattern Count by up to 50% and Significantly Shortens ATPG Runtime

Highlights: Thorough evaluation of TetraMAX II demonstrated significant reductions in both pattern count and runtime without impacting test coverage TetraMAX II was up and running in Toshiba's...